- Sectors

- Aerospace & Defense

- Big science

- Fintech

- Insights

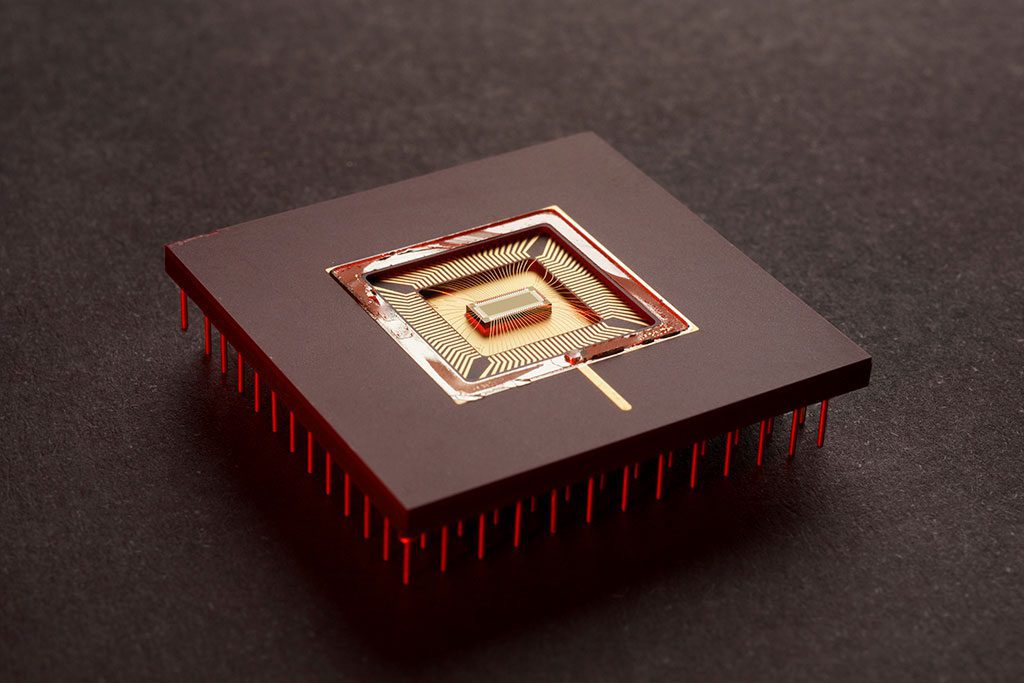

We provide analog, digital and mixed-signal microelectronics, including IP cores, ASIC, FPGA, ASSP and standard components. We deliver end-to-end solutions, from requirements definition, feasibility analysis and technology selection up to chip design, manufacturing and qualification as per the space standards.

We specialize in integrated circuits based on commercial technologies and hardened by design against the effects of cosmic and environmental radiation.

We are fabless and we provide the most suitable technology for each application: high voltage, high speed, low power… Our expertise goes from mature nodes up to deep submicron (22nm and below).

Our space microelectronics developers create systems capable of meeting the demanding needs and performance of space missions, so that they withstand complex conditions during the launch process and operate reliably in the adverse conditions of radiation in space.

Contact us, set us a challenge and discover everything we can offer you.