- Sectores

- Aeroespacio y defensa

- Industria de la ciencia

- Fintech

- Sobre ARQUIMEA

- Actualidad

IMAGE COPYRIGHT: Airbus & ESA

El satélite EUTELSAT QUANTUM es un paso revolucionario para los satélites de comunicaciones comerciales, ya que ofrece una gran personalización y flexibilidad. Prestará servicios como la posibilidad sin precedentes de ser reconfigurado en órbita en cuanto a cobertura, frecuencia y potencia, lo que permitirá un reajuste completo de la misión, incluida la posición orbital. El satélite desarrollado por Airbus junto con la ESA incluye una pionera carga útil de antena activa multihaz que resulta una novedad en las comunicaciones comerciales por satélite en Europa.

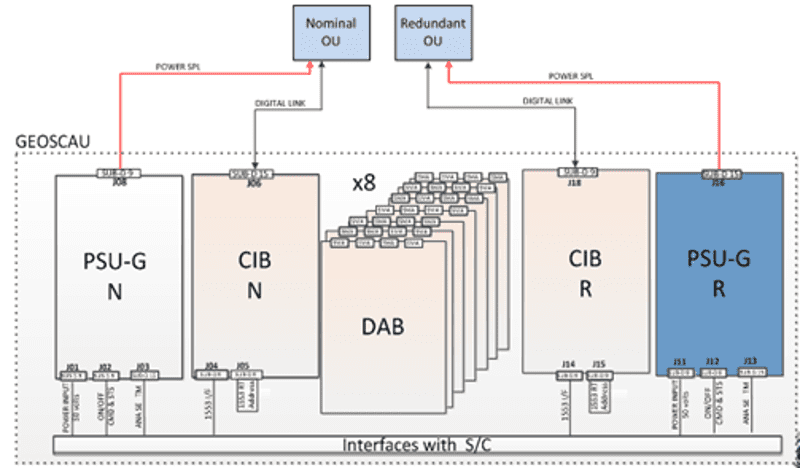

La Unidad de Acondicionamiento de Señales de Geolocalización (GEO-SCAU, por sus siglas en inglés) se basa en dos complejas FPGA (Matrices de Puertas Lógicas Programables en Campo) para ejecutar la funcionalidad de la Tarjeta de Captura de Interfaz (CIB, por sus siglas en inglés) y la Tarjeta de Adquisición Digital (DAB, por sus siglas en inglés).

ARQUIMEA se le encargó el diseño y la codificación de dos FPGA RTAX-S de Microsemi resistentas a la radiación y su posterior verificación conforme a la norma espacial ECSS-Q-ST-60-02C.

COPYRIGHT: ANDRA (Agence Nationale pour la gestion des déchet radioactifs)

La funcionalidad de las FPGA se puede resumir como sigue:

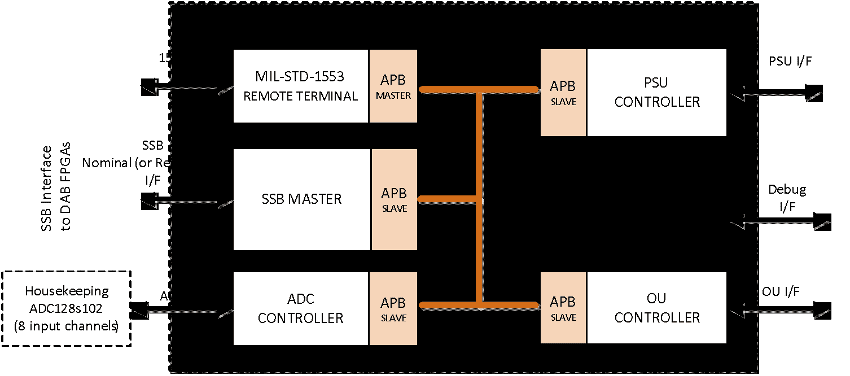

FPGA DE LA CIB

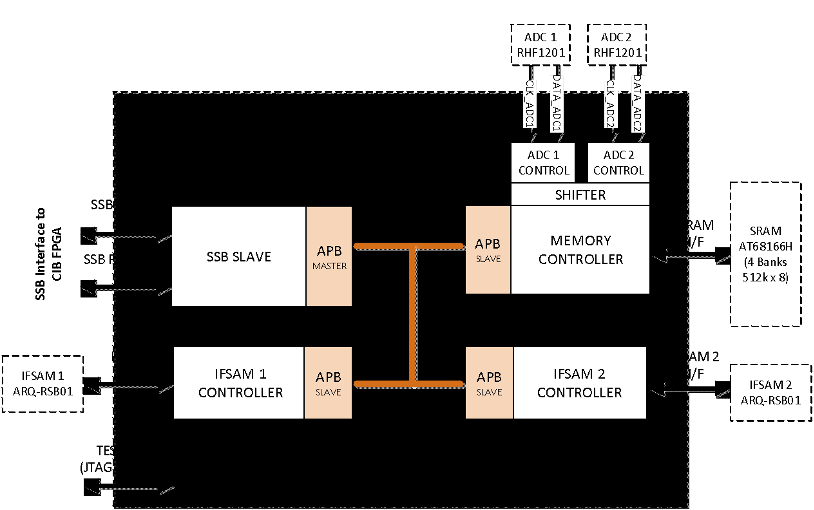

FPGA DE LA DAB

Desarrollo del complejo diseño digital de la FPGA considerando diferentes interfaces en conjunción con diferentes protocolos de comunicación, y gestión de telecomandos y telemetrías.

ARQUIMEA implantó la lógica requerida en las dos FPGA de vuelo siguiendo un flujo de desarrollo basado en el estándar espacial ECSS-Q-ST-60-02C, incluyendo el diseño, la programación y la verificación.

El diseño se completó satisfactoriamente para los dos dispositivos FPGA. Se implantó y validó un prototipo mediante la programación de un dispositivo ProASIC3, mientras que los modelos de vuelo se produjeron y validaron en los dispositivos RTAX-S calificados para el espacio de Microchip. La programación de la FPGA y la validación del hardware fueron realizadas por ARQUIMEA en las instalaciones de Airbus.

Las FPGA se montaron en el sistema GEO-SCAU y el satélite EUTELSAT QUANTUM completó la fase de calificación. El lanzamiento de la nave espacial está previsto para 2020.